I3C, o futuro substituto dos barramentos I2C e SPI?

- por Sergio Prado

Atualmente, os barramentos I2C e SPI são os mais utilizados para conectar dispositivos externos (sensores, EEPROM, etc) a microcontroladores e SoCs. Mas a vida útil deles pode estar no fim, porque vem aí o barramento I3C.

O I2C é um barramento bem antigo, criado em 1982 pela Philips Semiconductor, com mais de 35 anos de vida! É um barramento simples, com apenas duas linhas de comunicação: clock (SCL) e dado (SDA). Esta simplicidade facilita o projeto da placa de circuito impresso, mas traz algumas desvantagens. O endereçamento é feito no protocolo, sendo tipicamente limitado a 7 bits, o que permite um máximo de 127 dispositivos conectados ao barramento. Outra grande desvantagem do barramento I2C é a velocidade de comunicação, tipicamente de 100Kbit/s a 400Kbit/s.

O barramento SPI também é bastante antigo, criado em meados da década de 80 pela Motorola. Sua arquitetura é mais complexa, exigindo 4 linhas de comunicação: clock (SCLK), master output (MOSI), slave output (MISO) e slave select (SS). Comparado ao I2C, sua grande desvantagem é a complexidade do projeto da placa de circuito impresso, principalmente se você tiver mais de um dispositivo SPI conectado ao barramento, o que vai exigir pinos extras de I/O para fazer a seleção do slave (chip select). Mas a velocidade de comunicação é muito maior, podendo chegar a 60Mbit/s, dependendo do clock da CPU e do dispositivo. O barramento SPI também consome menos energia que o barramento I2C.

Qual o problema destes barramentos? Nenhum. A questão é que eles se complementam, cada um resolvendo um domínio de problemas diferentes. O I2C é mais simples, porém mais lento. O SPI é mais rápido e consome menos energia, porém pode aumentar bastante a complexidade do projeto de hardware.

Além disso, ambos os barramentos I2C e SPI não suportam interrupções. Isso significa que será necessário o uso de pinos extras de I/O para receber interrupções de dispositivos conectados a estes barramentos. O mesmo vale para gerenciamento de energia. Não existe nenhum suporte nestes barramentos para colocar um dispositivo em modo de baixo consumo, e normalmente a implementação de gerenciamento de energia é feita por fora, via algum registrador do dispositivo ou pino extra de I/O.

E se eu disser à vocês que o barramento I3C tem tudo isso e muito mais? :-)

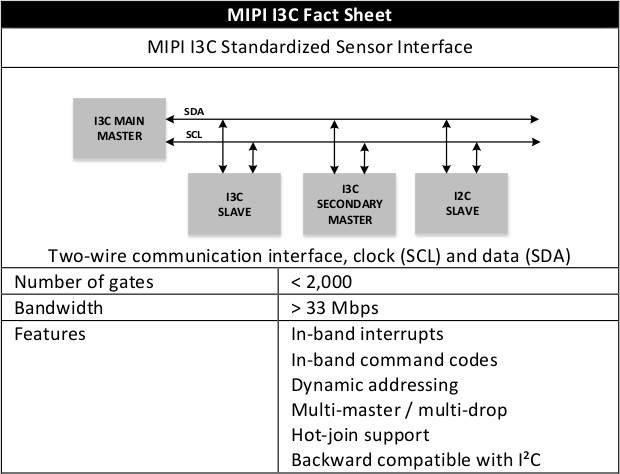

O I3C é um padrão de barramento criado pela MIPI Alliance, a mesma responsável por outros barramentos bastante comuns como o CSI (Camera Serial Interface) para câmeras. O nome I3C vem de Improved Inter Integrated Circuit, e seu desenvolvimento começou em meados de 2014. A primeira versão da especificação foi lançada no começo de 2017, e em dezembro de 2017 o padrão foi aberto ao público, o que deve incentivar seu uso no projeto de novos circuitos integrados.

O I3C traz o melhor dos mundos I2C e SPI. É simples, e assim como o I2C, utiliza apenas duas linhas de comunicação: clock (SCL) e dado (SDA). Mas é muito mais rápido que o I2C, com velocidades comparáveis ao SPI, começando em 10Mbit/s e podendo passar de 30Mbit/s!

O I3C possui suporte à interrupção integrado ao barramento de comunicação (In-Band Interrupt). Ou seja, você não precisa de pinos extras de I/O para receber uma requisição de interrupção de um dispositivo I3C. O mesmo acontece com gerenciamento de energia. Já existe suporte integrado no barramento para gerenciamento de energia e modos de baixo consumo de dispositivos I3C.

O endereçamento dos slaves é dinâmico. Isso significa que, durante a inicialização do barramento, o master atribui dinamicamente endereços aos slaves conectados ao barramento. Além disso, cada dispositivo I3C possui um número identificador de 48 bits chamado Provisional ID, que contém informações sobre o dispositivo, incluindo o fabricante e o part number. Desta forma, o master consegue identificar (enumerar) em tempo de execução os dispositivos conectados ao barramento. Ou seja, não será necessário declarar dispositivos I3C no device tree! :)

O barramento I3C é hotplug (eles chamaram esta funcionalidade de hot-join). Ou seja, você pode conectar um dispositivo no barramento I3C dinamicamente, em tempo de execução.

Além disso tudo, o I3C é compatível com o I2C. Isso significa que, se foram tomados alguns cuidados com o projeto da placa de circuito impresso, dispositivos I2C irão funcionar em um barramento I3C!

Tem uma tabela bem bacana disponível na documentação que resume o funcionamento do barramento, diferenciando o I3C, I2C e SPI (clique na tabela para abrir uma versão de melhor resolução):

Por falar em documentação, este Whitepaper resume as características do barramento, existe um FAQ de leitura rápida que pode tirar muitas dúvidas sobre seu funcionamento, além claro da especificação completa que pode ser baixada no site da MIPI Alliance.

Ainda não existem dispositivos compatíveis com I3C, mas o kernel Linux está em vias de suportá-lo com a segunda revisão dos patches enviada recentemente pelo Boris Brezillon, e atualmente existem algumas implementações de IP do I3C, como este da Silvaco e este da Cadence.

A especificação do I3C foi desenvolvida pelo MIPI Sensor Working Group da MIPI Alliance, que possui entre seus membros empresas gigantes como AMD, Broadcom, Google, Cadence, Intel, Lattice, MediaTek, Mentor Graphics, Nvidia, NXP, Qualcomm, Sony, STMicroelectronics, etc.

Não dá para negar a força destas empresas no mercado de tecnologia e semicondutores, e somando a isso o fato do padrão ser aberto ao público e não ter nenhum tipo de royalties associado, é bem provável que a partir de 2018 comecem a aparecer dispositivos, microcontroladores e SoCs compatíveis com este barramento.

Quem viver, verá! :)

Um abraço,

Sergio Prado